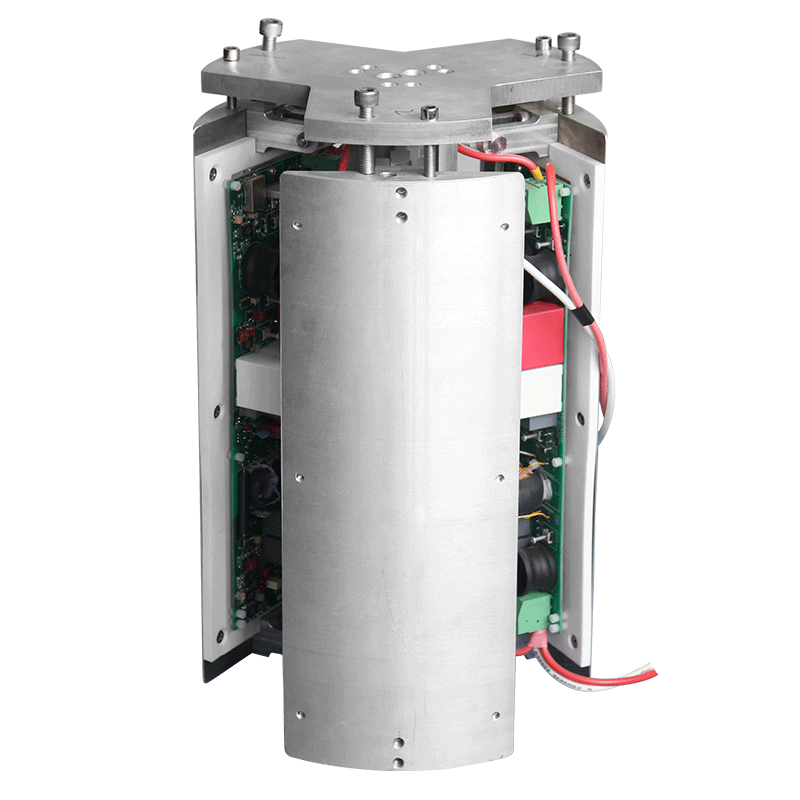

高精度低纹波电源的设计要点与核心技术解析

在精密仪器、医疗设备、半导体制造等领域,电源输出的微小纹波可能导致信号失真、时钟抖动或系统性能下降。传统方案采用“DC/DC转换器+LDO稳压器”的组合实现低噪声输出,但LDO在大电流场景下会产生显著功率损耗(典型应用增加约1.5W),引发热管理难题。现代设计通过创新拓扑与系统级优化,在保证低纹波的同时提升效率。

一、电源拓扑结构优化

1. LDO的替代方案

传统LDO虽能有效抑制高频噪声,但其压降损耗(≥1V)限制了效率。新型方案采用集成噪声抑制的开关稳压器,在反馈环路中嵌入模拟带隙基准低通滤波器(如CNR/SS引脚连接电容),直接降低开关噪声。此类设计可减少30dB以上的纹波,同时避免LDO的热损耗问题。

2. 双路并联互补技术

高压电源中,两路相位差90°的半桥逆变电路并联输出,利用电压波形互补特性抵消脉动分量。实验证明,该结构在13kHz开关频率下可使纹波峰峰值降低50%以上,同时减少输出端滤波电容容量需求。

二、关键元件选型与参数设计

1. 滤波元件特性要求

滤波电容的ESR(等效串联电阻)和ESL(等效串联电感)直接影响高频噪声抑制能力。推荐组合使用X7R/X5R陶瓷电容与低ESR钽电容,避免单纯追求大容量。例如在5V/2A输出时,需计算电容容量(公式:$C = kT/2R$),典型值达20,000μF。

2. 电感与频率协同设计

储能电感需优先考虑工作频率下的Q值而非仅关注感量。增大电感或提高开关频率可抑制纹波,但需平衡效率:电感值加倍或频率提升至MHz级可显著平滑输出,但需配合低损耗磁芯材料防止饱和。

三、纹波抑制核心技术

1. 多级滤波架构

LC低通滤波:在稳压输出端增加π型滤波器(如33μH功率电感并联4,700μF电容),截止频率需低于开关基频。实测表明该结构对100kHz以上纹波衰减>40dB。

有源滤波:通过运算放大器引入反馈补偿,动态调整滤波参数,适用于宽负载变化场景。

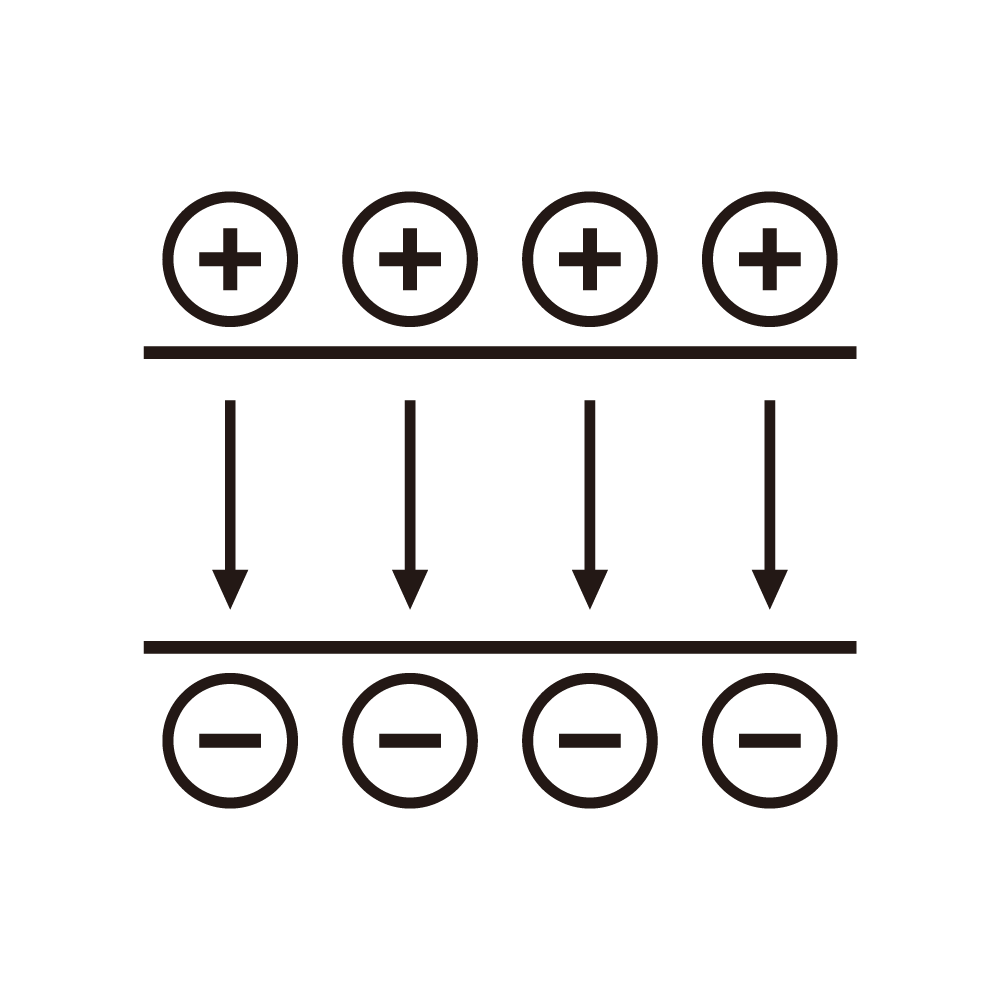

2. 多相调节技术

多相并联的开关稳压器将负载分配到多个相位,等效提升开关频率。例如4相交错并联可使纹波频率提高4倍,同时降低单路电流应力,适用于输出电流>10A的高精度系统。

四、PCB设计与布局优化

敏感路径隔离:电压采样回路需采用开尔文连接,直接连接负载点,减少走线阻抗影响(目标精度±8%)。

功率路径最短化:开关环路面积控制在<1cm²,输入电容紧邻IC引脚,取样网络与反馈回路避免穿越高频区域。

层叠结构:多层板设计中分配完整地平面,分割模拟/数字区域,并使用屏蔽层隔离噪声耦合。

五、控制策略创新

1. 动态电压调整(DVS)

根据负载瞬态预测,动态微调输出电压(例如轻载时升压5%)。当负载突增时,电压从5.2V降至4.95V而非传统方案的5V→4.75V,将偏差压缩在1%以内。

2. 数字闭环控制

采用MCU或DSP实现自适应PID算法,结合高精度ADC/DAC(16位以上)实时调节PWM占空比。数字控制支持参数在线整定,适应不同温度与负载工况。

> 设计权衡原则:半导体设备电源需满足纹波<50mV、调整率≤0.01%的要求。实现时需平衡:

> 效率与噪声:开关电源效率>90%但需多级滤波,线性电源噪声低但效率受限;

> 成本与密度:高频化减少元件尺寸但增加GaN等器件成本。

结语

高精度低纹波电源设计需融合电路拓扑创新、元件特性优化、先进控制算法三大维度。通过双路并联结构降低固有脉动、DVS技术补偿动态跌落、以及π型滤波器与PCB协同布局,可在不依赖LDO的条件下实现μV级噪声抑制。未来趋势将聚焦于宽禁带半导体应用与AI驱动的自适应控制策略,进一步突破效率与精度极限。