光刻机高压电源抗干扰设计的关键技术

光刻机作为半导体制造的核心设备,其高压电源的稳定性直接决定曝光精度与芯片良率。然而,高压电源在运行时易受电磁干扰(EMI)、地线噪声及高频开关噪声的影响,导致输出波动甚至系统失效。因此,抗干扰设计需从电源架构、电路布局、屏蔽接地及软件防护等多维度综合优化。

1. 电源滤波与隔离设计

高压电源的输入级需采用多级滤波网络:

• 交流滤波器:在电源入口设置低通滤波器,抑制电网传导的高频噪声(如浪涌、谐波),并选用穿心电容或三端电容降低引线电感的影响。

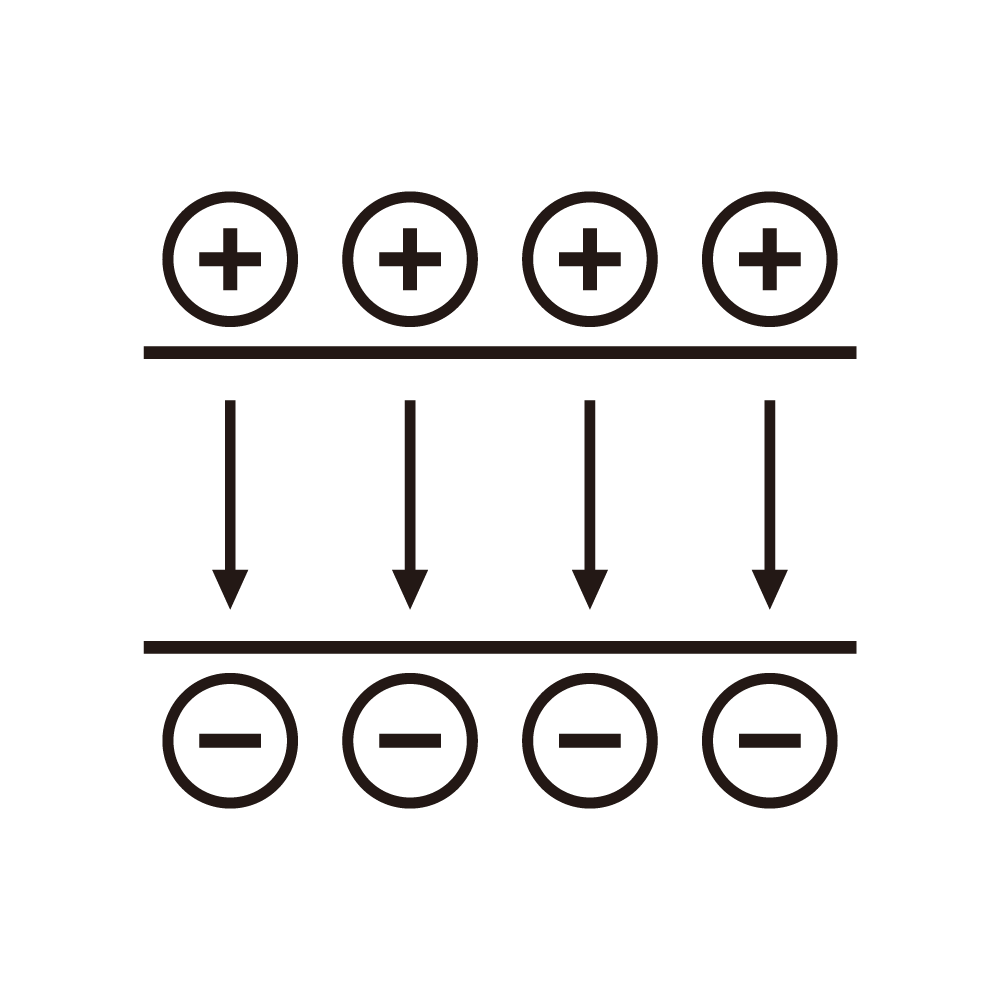

• 直流退耦:在整流电路后并联双电容(10–100 μF电解电容+0.01–0.1 μF陶瓷电容),分别吸收低频纹波与高频瞬变。

• 隔离技术:采用静电屏蔽变压器,初级与次级间增加铜箔屏蔽层并单点接地,阻断共模噪声传播;功率电路与控制电路通过光耦隔离,消除地环路干扰。

2. 接地与屏蔽的系统性优化

• 分层接地策略:

• 模拟/数字地分离:高压电源的模拟电路(如稳压控制)与数字电路(如PWM控制器)分别铺设独立地线,最终通过磁珠或0Ω电阻单点汇接,避免公共阻抗耦合。

• 接地线低阻抗设计:地线宽度≥2–3 mm,并通过网格层(Mesh)降低阻抗;屏蔽层、机壳与安全地采用短粗导线(黄绿双色线)连接,接地电阻<4 Ω。

• 三维屏蔽结构:

高压模块采用全封闭金属屏蔽罩,内部高频元件(如开关管)增设局部铁氧体磁环;信号线使用双绞屏蔽线,屏蔽层双端接地以抑制辐射噪声。

3. PCB布局的电磁兼容性设计

• 分层布局:优先选用4层以上PCB,中间层专设电源层与地层,提供低阻抗回流路径;高压走线(如开关管至变压器)长度≤15 mm,避免90°折线。

• 去耦电容近场配置:每个IC芯片的电源引脚就近布置0.1 μF陶瓷电容,且电容焊盘直接连接电源层(Via-in-Pad工艺),减少引线电感。

• 敏感区域隔离:时钟电路、振荡器远离高压区域≥10 mm,周围增设地线包围;数字信号线与高压线垂直交叉布线,减小互感耦合。

4. 软件协同防护机制

• 看门狗与状态监控:通过硬件看门狗电路检测电源控制器的运行状态,异常时触发复位;ADC采样通道加入数字滤波(如中值滤波+滑动平均),抑制瞬态干扰。

• 逻辑校验与冗余:关键指令(如曝光触发信号)采用三取二表决逻辑;通信协议添加CRC校验与重传机制,防止数据因噪声畸变。

结论

光刻机高压电源的抗干扰设计需融合“隔离-滤波-屏蔽-接地”四重防护,同时通过PCB分层布局与软件容错机制形成纵深防御。随着光刻精度进入纳米级,未来需进一步研究高频磁场主动抵消技术及宽禁带半导体器件(如SiC)的高频噪声抑制模型,以应对更高功率密度下的电磁兼容挑战。