蚀刻设备高压电源负载匹配:精密工艺的核心挑战

一、负载匹配的技术原理

在等离子体蚀刻设备中,高压电源通过激发反应气体形成等离子体,其中的离子在电场作用下轰击材料表面实现刻蚀。负载匹配的核心在于阻抗匹配:

1. 能量传输最大化:当电源输出阻抗与等离子体负载阻抗共轭匹配时(实部相等、虚部相反),可实现功率传输效率最大化(>95%),避免反射波导致的能量损失。

2. 动态响应要求:等离子体阻抗随工艺过程实时变化(如气体电离率波动),电源需通过自动匹配器(如RF匹配网络)动态调整电容/电感值,维持阻抗实部稳定。

3. 高频特性挑战:在13.56 MHz射频系统中,波长(约22米)与传输线长度相当,失配会引发驻波,导致蚀刻均匀性下降±10%以上。

二、负载失配对蚀刻工艺的影响

1. 轮廓控制失效

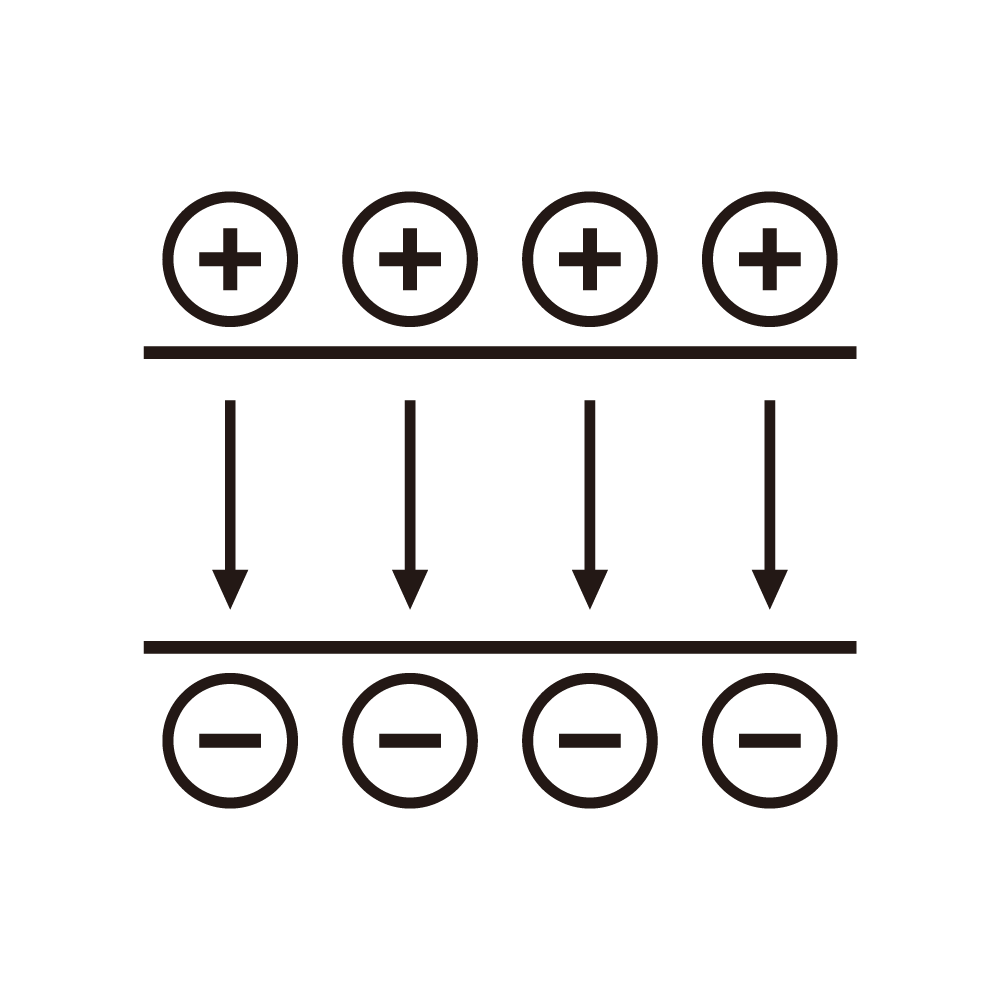

• 垂直度偏差:阻抗失配导致离子能量分布不均。例如高压电源输出波动±5%时,硅刻蚀侧壁角度可能偏离90°±2°,影响高深宽比结构的成型。

• 选择比下降:当基底膜(如SiC)与被刻蚀膜(如Low-k介质)的阻抗特性差异被忽略时,选择比从20:1降至5:1,造成底层损伤。

2. 微负载效应加剧

在小尺寸孔槽蚀刻中,阻抗失配引发局部电流密度差异,导致孔径≤100 nm区域的刻蚀速率比开放区域低30%,形成深度不一致性。

三、前沿匹配技术突破

1. 功率调制模式(Pulsed Bias)

• 双功率切换:在聚合物沉积(低功率10-50W)与刻蚀(高功率100-5000W)间以0.25-100 Hz频率切换,使基底膜聚合物厚度>离子侵入深度,保护层选择比提升3倍。

• 占空比优化:99%高占空比用于高深宽比蚀刻,1%低占空比用于表面平整工艺。

2. 碳化硅(SiC)功率器件应用

第三代半导体器件使电源响应时间缩短至微秒级,支持40 kHz高频调制,匹配精度达0.1%,克服传统硅基器件开关损耗导致的延迟。

3. 数字孪生匹配系统

通过实时采集等离子体阻抗谱,在虚拟模型中预演匹配策略,将工艺调试时间缩短70%,良率提升至98%。

四、技术挑战与趋势

1. 纳米级工艺的匹配极限

3 nm制程要求蚀刻深度误差≤±1.5 nm,需开发亚毫秒级阻抗反馈系统,当前技术仍存在±5 nm波动。

2. 多物理场耦合设计

未来高压电源需协同优化电磁场(阻抗)、流体场(气体分布)、热场(温控),实现“一键匹配”智能控制。

蚀刻设备高压电源的负载匹配,是连接电气工程与半导体制造工艺的核心纽带。随着制程进入埃米时代,匹配技术将从“被动响应”向“主动预测”演进,成为突破摩尔定律瓶颈的关键赋能点。