静电卡盘高压电源谐振抑制技术:原理与创新方案

在半导体制造工艺中,静电卡盘(Electrostatic Chuck, ESC)是晶圆蚀刻、沉积等关键工序的核心夹具,其稳定性直接决定工艺精度。高压电源作为静电卡盘的能量来源,需提供±5kV以上的直流电压以产生静电力(约翰森-拉贝克效应),固定300mm晶圆。然而,高压电源与卡盘电极、等离子体负载及滤波电路构成的复杂系统易引发谐振现象,导致电压波动、晶圆位移甚至设备损毁。谐振抑制技术因此成为提升半导体良率的核心突破口。

谐振产生机制与影响

静电卡盘系统的谐振主要由三类因素耦合引发:

1. 电路参数非线性:高压电源输出的直流电压需通过LCL滤波器消除高频噪声,但LCL拓扑中电感(L)与电容(C)的相互作用易在特定频率下形成谐振点。例如,当电源载波频率(通常为kHz级)与LCL的固有频率重叠时,会激发电流振荡,造成输出电压纹波增大。

2. 负载动态扰动:等离子体工艺中,反应腔内的气体电离状态突变会导致负载阻抗在300%范围内波动,引发高压电源的瞬时过载,进一步放大谐振幅值。

3. 多物理场耦合效应:静电吸附过程产生的焦耳热与晶圆-卡盘界面的接触热阻(波动幅度达20-30%)相互作用,形成热-电反馈回路,加剧谐振频率漂移。

此类谐振的直接影响包括:晶圆局部温度漂移(>5℃)、吸附力不稳(±3%偏差),最终导致刻蚀线宽均匀性恶化(CDU>0.8nm)。

谐振抑制的核心技术路径

为应对上述挑战,业界从电路拓扑优化、控制算法升级及材料创新三方面突破:

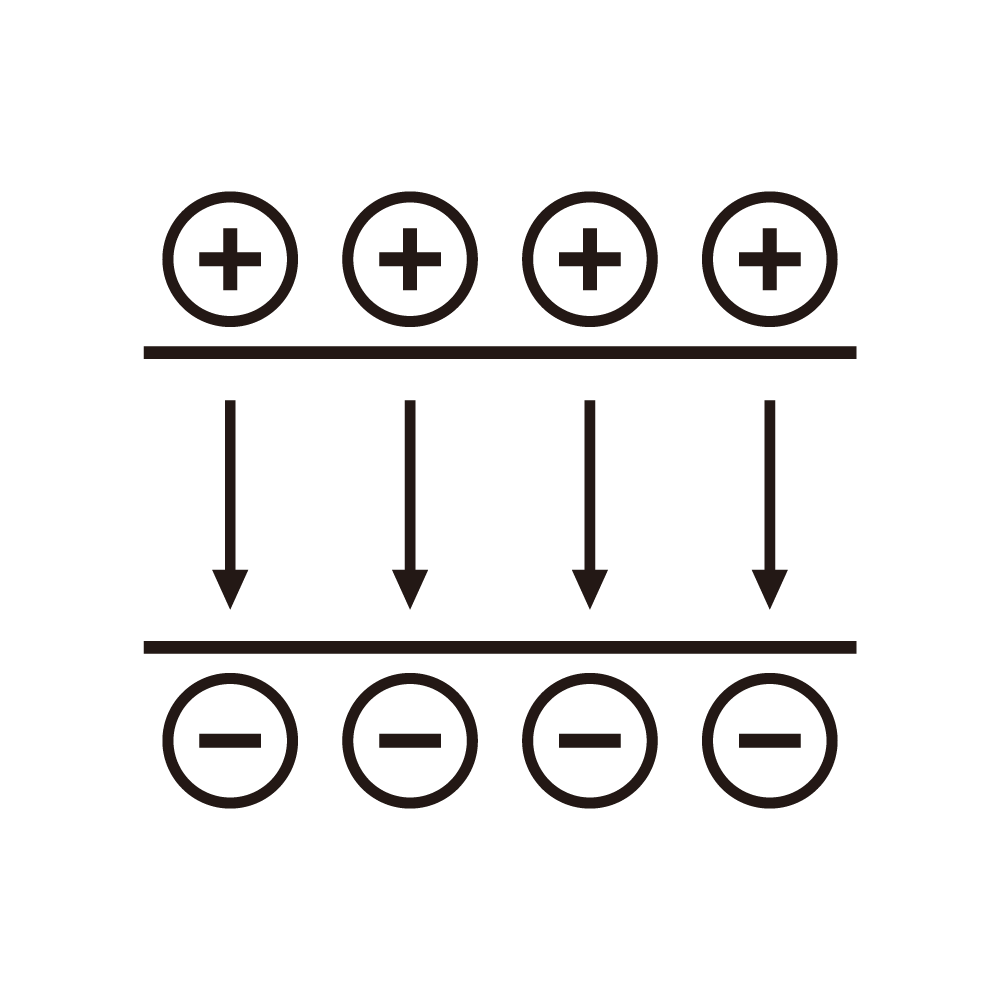

1. 高频采样与动态调制技术

• 多脉冲采样控制:在单个三角载波周期内进行N次等间隔电流/电压采样(N≥5),通过实时坐标变换(3s/2r)生成旋转坐标系下的直轴分量(id/iq)。结合模型预测控制(MPC)算法,提前300ms预判谐振趋势,动态调整PWM调制信号,将谐振能量抑制在毫秒级响应时间内。

• 虚拟电阻阻尼:在数字控制环中植入虚拟阻抗模型,替代物理阻尼电阻,避免传统无源阻尼的能耗问题。实验表明,该方法可将LCL谐振峰衰减40dB以上,且系统效率提升5%。

2. 复合电极结构与场协同设计

• 蜂窝电极阵列:采用主-子电极分层设计,主电极(直径200μm)负责静电吸附,子电极(直径50μm)嵌入热敏材料执行局部温度补偿。当检测到谐振引发的热点时,子电极自动调节局部电场强度,实现热场均一性(±0.08℃)。

• 梯度介电层:表层覆盖高导热氮化铝(κ=180W/mK)快速导离焦耳热,底层采用高介电氮化硅(ε_r=7.5)阻断电场穿透,从源头上减少电场-热场耦合扰动。

3. 量子传感与智能反馈系统

• 纳米级温度监测:集成金刚石氮空位(NV)色心传感器,实现1μm空间分辨率与0.01℃/√Hz的温敏精度,抗等离子体干扰能力较传统RTD传感器提升100倍。

• CNN热场重构:基于卷积神经网络训练热分布图像,动态映射晶圆表面温度场,通过闭环控制补偿95%以上的热畸变,使刻蚀速率波动率降至±0.7%。

技术演进趋势

未来谐振抑制技术将向多尺度融合方向发展:

• 仿生热管理:模拟生物结构(如北极熊毛发)开发各向异性导热材料,实现轴向/径向热导率比>100。

• 光子-声子调控:利用表面等离激元(SPP)定向传输热能,结合声子工程抑制晶格振动损耗,理论热导率可提升10倍。

• 数字孪生平台:构建高压电源-静电卡盘系统的多场耦合虚拟原型,通过实时仿真预判谐振风险,缩短工艺开发周期80%。

结语

谐振抑制技术是高压电源在半导体高端装备中应用的“安全阀”。通过电路-材料-算法的协同创新,新一代谐振抑制方案不仅解决了晶圆吸附稳定性问题,更推动了刻蚀精度进入亚纳米时代。随着量子传感与人工智能的深度嵌入,静电卡盘系统将向零谐振、零热扰动的终极目标迈进。