静电卡盘高压电源介质界面优化研究

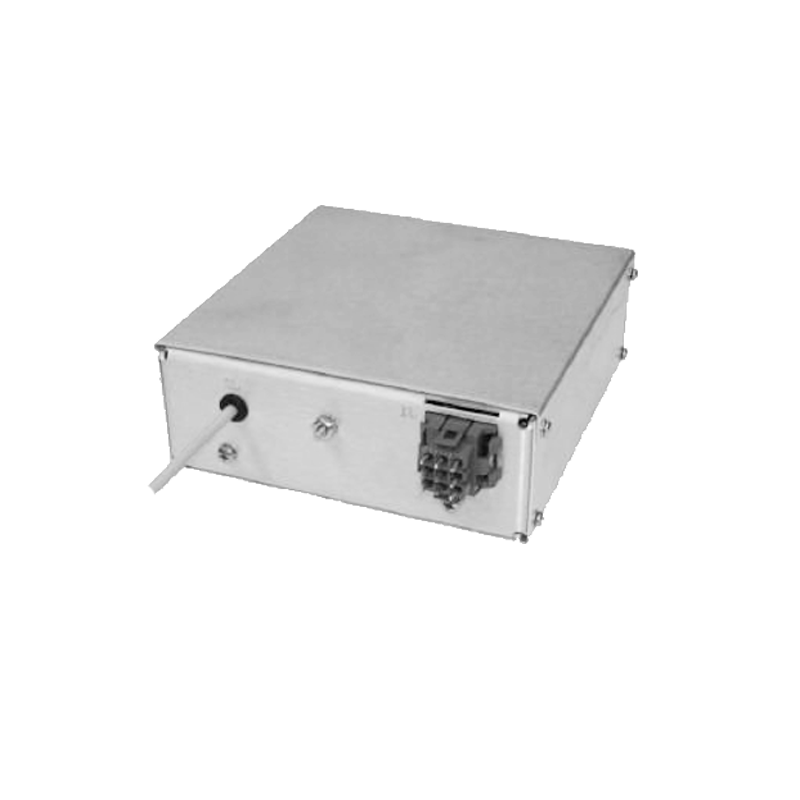

静电卡盘(Electrostatic Chuck, ESC)作为半导体制造中的核心部件,其性能依赖于高压电源与介质界面的协同作用。介质界面作为静电场传递的关键载体,其材料特性、结构设计及电热稳定性直接影响晶圆吸附力分布、定位精度及工艺重复性。本文从介质材料优化、界面控制技术及系统级协同设计三个维度,探讨高压电源驱动下介质界面的优化路径。

一、介质界面的核心挑战

静电卡盘通过高压电源在介质层与晶圆间建立静电场,产生库仑力或约翰森-拉贝克力(Johnson-Rahbek force)。然而,介质界面面临多重挑战:

1. 电热耦合效应:高压电源的输出温漂(如温度每波动10℃,输出电压漂移0.15%)导致吸附力波动,增加晶圆脱附风险。

2. 介电性能极限:传统氧化铝(Al₂O₃)介质层介电常数有限(ε≈9~10),限制吸附力提升,且高温下体积电阻率变化引发电荷泄漏。

3. 界面微观缺陷:介质层表面微裂纹或孔隙在高压电场下诱发局部放电,加速材料老化并污染工艺环境。

二、介质材料优化策略

1. 高介电常数材料应用

• 氮化铝(AlN)基复合材料:通过掺杂调控体积电阻率(如AlN-SiC体系),在保持高导热性(≥180 W/m·K)的同时,将介电常数提升至ε>10,吸附力较传统材料增强40%。

• 多层复合介质结构:采用梯度化设计(如Al₂O₃/AlN叠层),表层高硬度材料抵御等离子体腐蚀,底层高介电材料优化电场分布,实现吸附力均匀性(波动<±0.8%)。

2. 表面功能化涂层

• 抗等离子体涂层:通过PECVD沉积类金刚石碳(DLC)或氮化硼(BN)薄膜,厚度控制在微米级,降低表面侵蚀率并抑制颗粒污染。

• 微纳结构设计:在介质层表面刻蚀微槽阵列(深度5~20μm),增大有效吸附面积,并通过边缘电场强化效应提升局部吸附力。

三、界面控制技术突破

1. 温度-电压协同补偿

• 二阶曲率补偿电路:采用PTAT(正温度系数)与CTAT(负温度系数)电流叠加,将高压电源基准电压温漂从35ppm/℃压缩至3ppm/℃,确保25~100℃温域内输出电压漂移<0.005%。

• 热阻传导优化:集成GaN基低热阻开关器件与热敏电阻反馈网络,抑制IGBT结温波动,使电源效率>92%、温升ΔT<15℃。

2. 动态阻抗匹配技术

• 真空腔内气体介电常数受温度影响(Δε/ΔT≈0.05%/℃),导致ESC等效容性负载变化。基于FPGA的实时LC匹配网络可监测负载相位角(精度±0.1°),在200μs内完成谐振频率补偿,将吸附力波动从±5%降至±0.8%。

3. 边缘电场优化算法

• 通过有限元仿真(如COMSOL)建立介质层-晶圆界面电场模型,优化电极边缘的场强分布,减少电场畸变。实验表明,弧形电极设计使边缘吸附力提升25%,避免晶圆边缘翘曲。

四、系统级协同优化路径

介质界面性能需结合高压电源架构升级:

• 多电平拓扑结构:采用半桥串联电路替代机械继电器,实现极性切换时间<300ms(传统方案>1s),支持任意波形输出以适应复杂工艺需求。

• 数字孪生预测模型:集成电-热-力多物理场耦合仿真,预演不同工艺参数(如射频功率、气压)下的界面行为,动态调整高压输出策略。

结论

静电卡盘高压电源的介质界面优化是材料科学、电力电子与控制算法的交叉创新。通过高介电复合材料、温度-电压协同补偿及动态阻抗匹配技术的融合,可构建接近“温度无关性”的吸附系统。未来,宽禁带半导体器件与人工智能驱动的实时调控将进一步推动纳米级工艺精度的边界,为半导体制造提供更稳定的“无形之手”。