蚀刻设备高压电源射频直流耦合优化技术探析

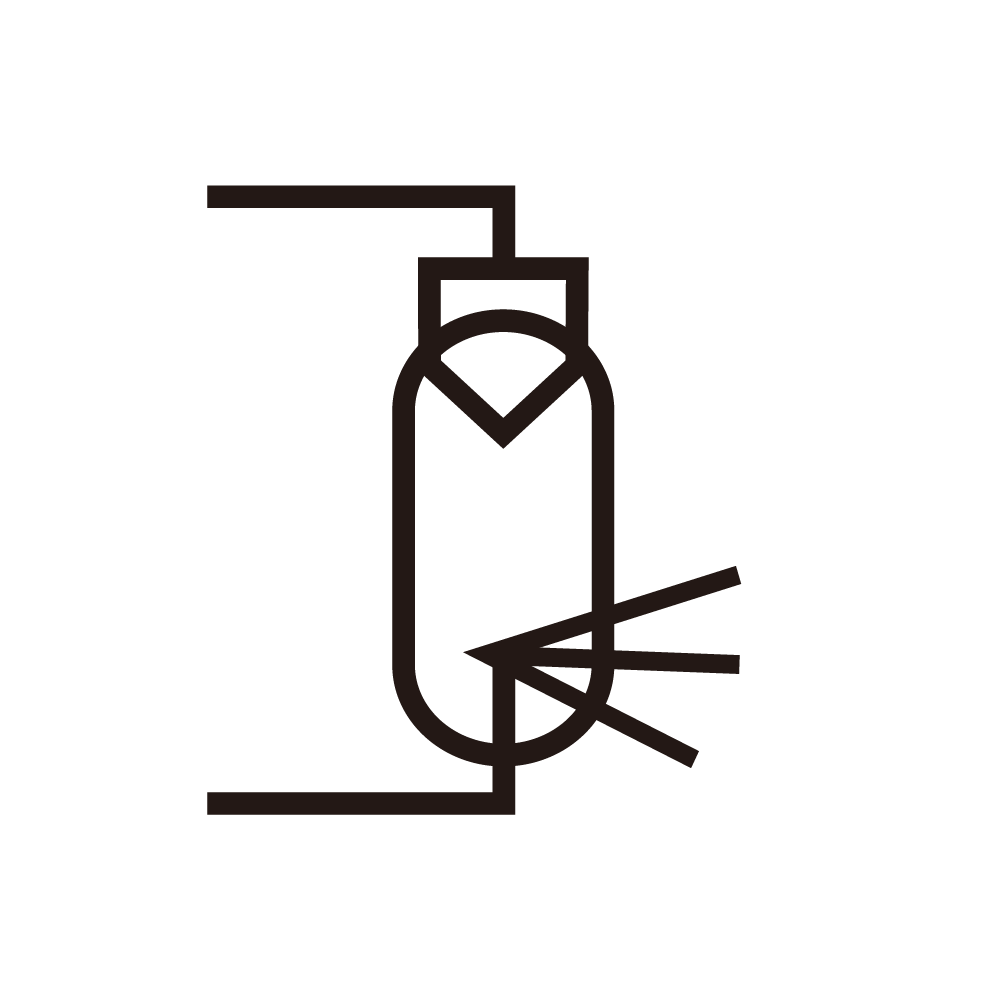

在半导体制造的蚀刻工艺中,高压电源作为等离子体生成与能量控制的核心部件,其射频(RF)与直流(DC)信号的耦合性能直接决定蚀刻精度、速率及晶圆均匀性。随着先进制程向7nm及以下节点推进,传统高压电源的RF-DC耦合方式逐渐暴露出阻抗失配、干扰叠加、能量损耗等问题,导致等离子体密度波动幅度超±5%,晶圆蚀刻均匀性偏差达3.2%,成为制约工艺良率提升的关键瓶颈。因此,针对蚀刻设备高压电源的RF-DC耦合优化,已成为半导体装备技术升级的核心方向之一。

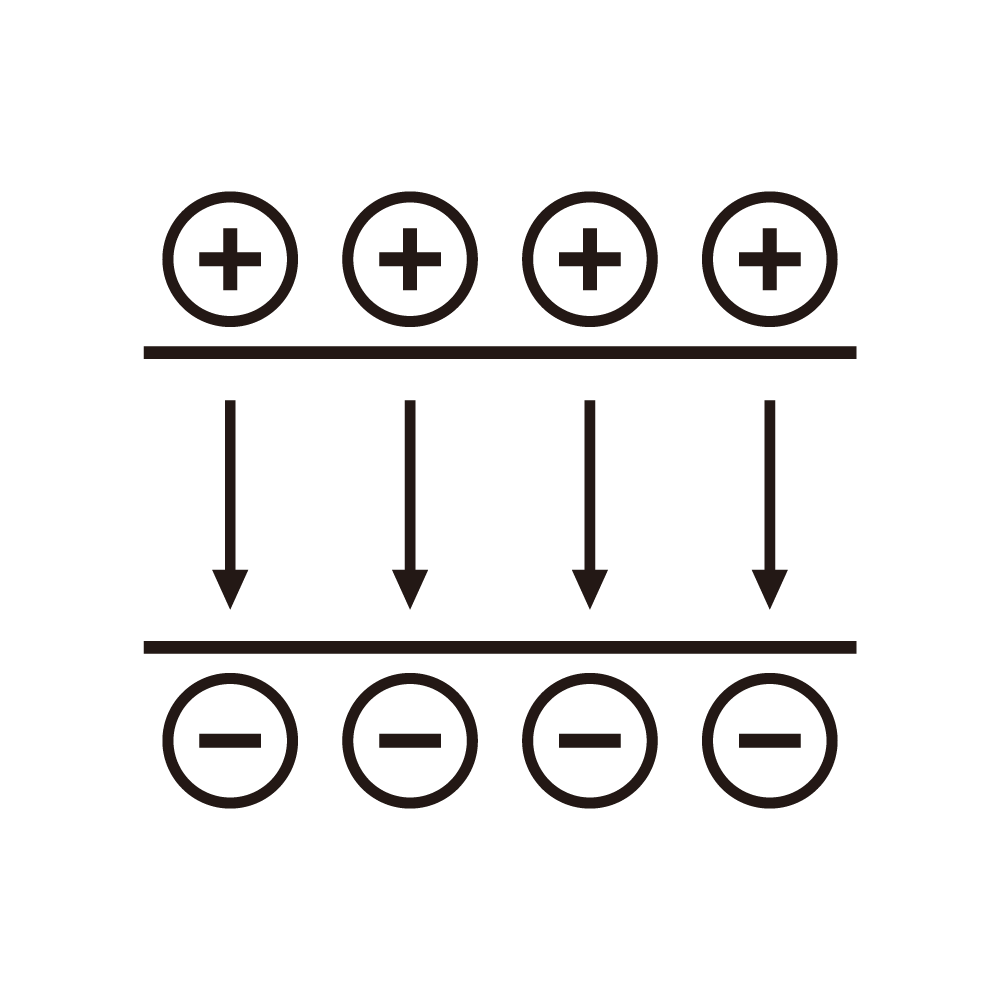

传统RF-DC耦合结构的核心痛点集中于三个维度:其一,RF信号(通常为13.56MHz或27.12MHz)与DC高压(数百至数千伏)共用传输路径时,易因阻抗特性差异产生能量反射,导致电源转换效率低于85%;其二,RF高频信号会通过寄生电容耦合至DC回路,引发DC输出纹波增大,进而造成等离子体鞘层厚度不稳定,影响蚀刻线宽精度;其三,耦合节点的寄生电感与电容会延长信号响应时间,当蚀刻工艺需求动态调整能量输出时,电源无法快速匹配等离子体负载变化,导致刻蚀速率波动。

针对上述问题,RF-DC耦合优化需从拓扑设计、干扰隔离、动态匹配三方面构建技术方案。在拓扑优化层面,可采用“双路径-共节点”设计:将RF信号与DC高压通过独立传输通道输送至耦合节点,节点处采用低寄生参数的多层陶瓷电容作为耦合介质,缩短信号传输路径的同时,将寄生电感控制在10nH以下,提升信号响应速度。在干扰隔离层面,需构建多级屏蔽与滤波体系:在DC回路中串联高频扼流圈,阻断RF信号向DC电源端反向耦合;在RF路径中增设带阻滤波器,抑制DC高压引入的低频干扰;同时采用金属屏蔽罩包裹耦合模块,降低外部电磁环境对耦合性能的影响,最终使DC输出纹波控制在5mV以内。在动态匹配层面,引入基于数字信号处理器(DSP)的阻抗自适应算法,实时采集等离子体负载阻抗变化数据,通过调整RF匹配网络的LC参数与DC高压的输出幅值,实现RF-DC能量耦合的动态平衡,使阻抗失配系数维持在0.1以下。

从应用效果来看,优化后的高压电源在12英寸晶圆蚀刻工艺中表现出显著性能提升:电源转换效率提升至92%以上,降低了设备能耗;等离子体密度波动幅度缩小至±2%,晶圆内蚀刻均匀性偏差降至1.8%,满足先进制程对蚀刻精度的要求;同时,设备平均无故障时间(MTBF)延长30%,减少了生产线停机维护成本。此外,该优化方案具备良好的工艺兼容性,可适配干法蚀刻、湿法蚀刻等不同工艺需求,为半导体制造装备的国产化升级提供了关键技术支撑。

未来,随着蚀刻工艺向更高精度、更高效率方向发展,RF-DC耦合优化还需结合人工智能算法,实现负载变化的预判式匹配,进一步提升高压电源的动态响应能力,为半导体先进制程的持续突破提供稳定的能量控制保障。