静电卡盘高压电源介质界面陷阱效应抑制的技术应用与实践

在半导体制造向7nm及以下先进工艺节点演进的过程中,静电卡盘(ESC)作为晶圆夹持与精准定位的核心组件,其性能稳定性直接决定光刻、刻蚀等关键制程的良率。高压电源作为ESC的“能量中枢”,需持续输出稳定电场以实现晶圆的无损伤夹持,但介质界面陷阱效应的存在,常导致电场畸变、电荷积累失衡,成为制约ESC性能提升的核心瓶颈。

介质界面陷阱效应的本质的是ESC介质层(如Al₂O₃、SiO₂复合层)与电极/晶圆界面处的缺陷态(含悬挂键、杂质能级、氧空位等)对载流子的捕获与释放过程。当高压电源输出电压时,部分载流子被界面陷阱捕获后形成空间电荷区,不仅会削弱有效夹持电场强度,还会导致电场分布不均——表现为晶圆边缘与中心的夹持力差异可达15%以上,进而引发晶圆偏移、制程图形失真等问题。此外,陷阱电荷的长期积累还会加速介质层老化,缩短高压电源与ESC的协同使用寿命。

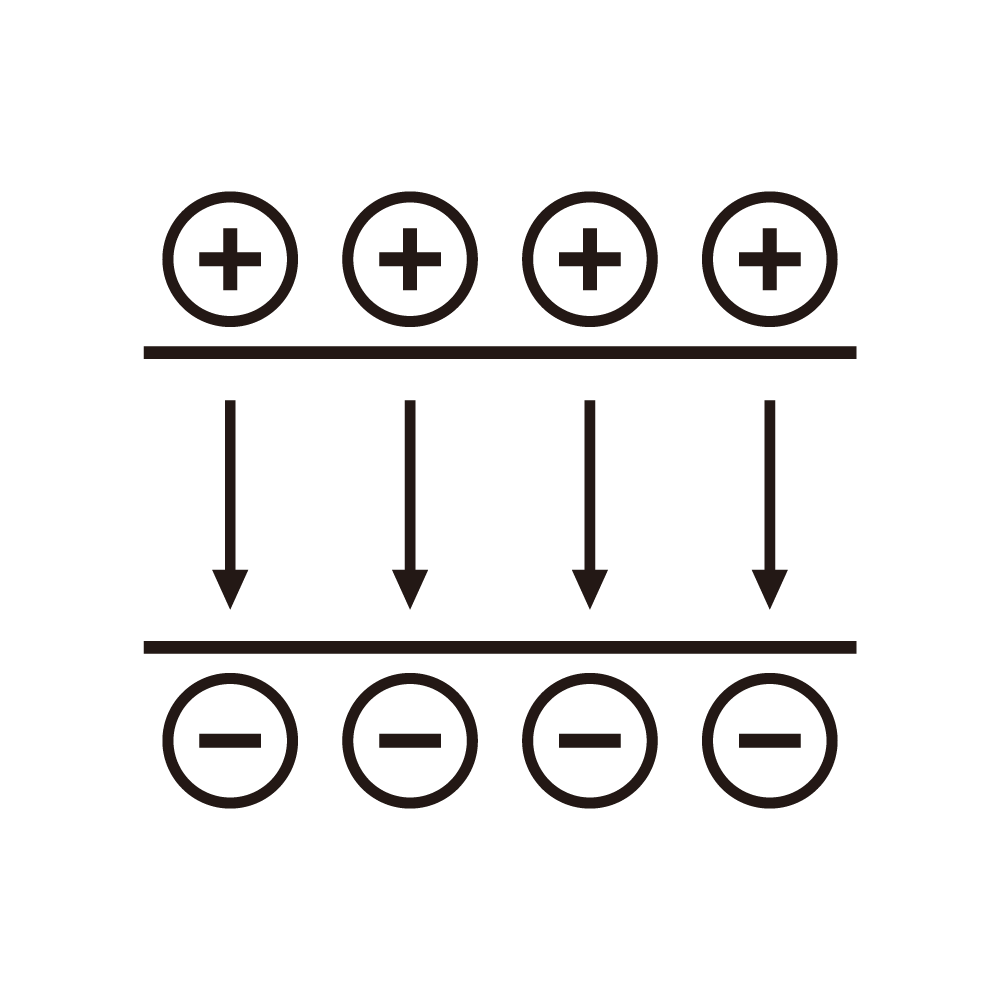

针对这一问题,需从“材料优化-电源设计-控制算法”三维度构建抑制体系。在材料层面,通过原子层沉积(ALD)工艺制备致密化介质层,可将界面缺陷密度降低40%以上;同时引入Mg²+、Y³+等掺杂离子,能有效抑制氧空位形成,减少陷阱态的产生源。在电源拓扑设计上,采用谐振型高压拓扑替代传统硬开关拓扑,可将开关噪声降低25dB,避免高频噪声激发界面陷阱的载流子捕获行为。而在控制算法层面,自适应电荷补偿算法的应用尤为关键:该算法通过实时监测界面电荷密度(基于电容耦合原理),动态调整高压电源的输出波形——将传统方波优化为阶梯波,在电压上升阶段缓慢注入电荷,给陷阱态载流子释放留出时间,使夹持力波动范围控制在±1%以内。

从应用效果来看,上述抑制技术已在3D NAND刻蚀制程中实现验证:采用优化后的高压电源-ESC系统,晶圆的翘曲量从5μm降至1.2μm,刻蚀图形的线宽偏差缩小30%,制程良率提升8%-12%。这表明,介质界面陷阱效应的有效抑制,不仅能释放高压电源的性能潜力,更能为先进半导体制程的稳定性提供关键支撑。

未来,随着EUV光刻等技术对ESC夹持精度要求的进一步提升,高压电源的陷阱效应抑制技术将向“智能感知-主动调控”方向发展——通过集成AI算法预测陷阱电荷积累趋势,提前调整电源参数,实现从“被动抑制”到“主动预防”的跨越,为半导体制造的精细化发展提供更可靠的能量保障。