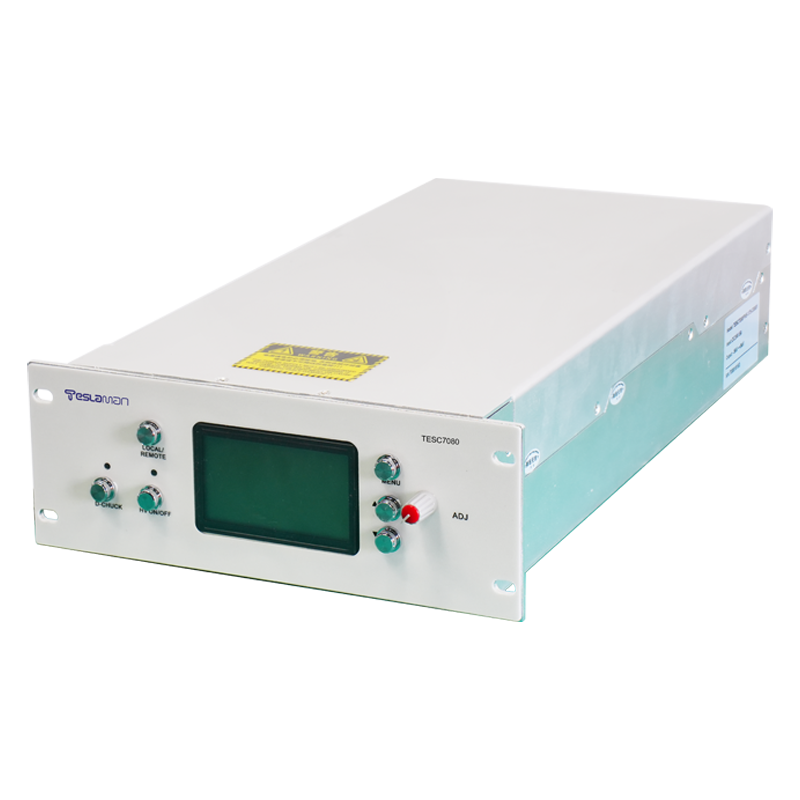

225kV镀膜电源纹波抑制研究

在高端光学镀膜、半导体薄膜沉积以及超导薄膜制备等真空镀膜工艺中,磁控溅射、电弧蒸发、离子束辅助沉积等技术常需要为靶材或基板施加高达数百千伏的直流偏压或脉冲偏压。其中,225kV直流高压常用于驱动大型磁控溅射靶或提供高能离子辅助。此类工艺对薄膜的微观结构、应力、成分及界面特性极为敏感。为镀膜电源供电的225kV直流高压,其输出纹波——即叠加在直流电平上的周期性或非周期性交流分量——是一个至关重要的性能指标。纹波电压会调制等离子体鞘层电位,导致轰击基板或生长薄膜的离子能量发生周期性波动。这种能量波动可能引起薄膜生长模式的不稳定,增加缺陷密度,导致膜层应力异常、光学性能(如折射率、吸收)不均匀,甚至影响薄膜的附着力和耐久性。因此,对225kV镀膜电源纹波的产生机制、传递路径及抑制方法进行深入研究,是获得高性能薄膜的必然要求。

纹波抑制研究首先需精确表征纹波的来源与频谱。对于225kV高压电源,其纹波主要来源于以下几个途径:

1. 工频及其谐波纹波:若电源采用工频变压器升压后整流滤波的方案,未能完全滤除的100/120Hz(两倍电网频率)及其谐波是主要的低频纹波来源。

2. 开关频率纹波:现代高频开关电源将工频交流首先转换为直流,再逆变为高频交流经变压器升压后整流。其开关频率(通常在数十kHz至数百kHz)及其边带谐波是纹波的主要高频成分。开关器件的非理想开关过程(如开关瞬态振铃)也会产生更高频的噪声。

3. 倍压整流电路固有的纹波:在多级倍压整流电路中,即使前端是纯直流,由于电容充放电的周期性,输出端也会存在与倍压级数和驱动频率相关的纹波。

4. 负载扰动引入的纹波:镀膜过程中的等离子体负载并非恒定,其阻抗会随工艺气体压力、功率、靶材状态等发生动态变化。这种负载变化会通过电源的闭环反馈或直接耦合,在输出电压上引入低频扰动纹波。

5. 外部电磁干扰耦合:电源附近的其他大功率设备(如射频电源、电机)产生的电磁干扰可能通过传导或辐射方式耦合到高压输出回路。

研究纹波抑制,需要建立电源系统的频域模型,分析从输入端到输出端的传递函数,识别纹波放大的关键节点。常用的抑制策略是分层、分级进行滤波和补偿:

输入级滤波与有源功率因数校正:在电源输入端使用EMI滤波器和有源PFC电路,不仅可以提高功率因数,还能显著平滑输入电流,减少输入侧引入的低频纹波。

拓扑选择与优化:采用全桥、半桥等对称拓扑可以减少变压器原边的直流偏磁,从而降低输出纹波。提高开关频率可以将纹波能量推向更高频段,便于后续滤波。采用多相交错并联技术,可以抵消部分纹波电流。

高频变压器与整流电路设计:优化高频变压器的绕制工艺,采用三明治绕法、屏蔽层等措施,以最小化漏感和分布电容,减少高频振铃。选择超快恢复二极管或同步整流技术,以降低整流环节的反向恢复噪声和损耗。

多级滤波网络设计:这是抑制输出纹波最直接有效的手段。在倍压整流电路的每一级以及最终输出端,都需要设计精密的LC或RC滤波网络。对于225kV高压,电感(抗流圈)的设计尤为关键,需要采用分段绕制、低损耗磁芯,并处理好自身分布电容对高频滤波效果的影响。电容需选用低等效串联电感和低损耗的高压陶瓷或薄膜电容。滤波器的参数需要通过仿真和实验确定,确保在关键的纹波频率点(如开关频率及其主要谐波)有足够的衰减,同时避免引入谐振点。

有源纹波补偿技术:这是一种更主动的抑制方法。通过高精度分压器实时采样输出电压中的纹波分量,经过反相放大后,通过一个辅助的功率放大器将反相的补偿信号注入到输出回路中,从而抵消原有的纹波。这种方法特别适合抑制特定频率(如工频)的纹波,但对补偿环路的带宽、相位精度和稳定性要求极高。

负载端局部去耦:在靠近镀膜腔室的高压引入端,并联一个低电感的高压电容组,可以为等离子体负载的动态变化提供局部的电荷缓冲,抑制由此反射回电源的电压扰动。

布局、屏蔽与接地:精心的PCB和系统布局,缩短高频大电流路径,对敏感电路和高压输出线进行屏蔽,以及采用科学的单点接地或混合接地策略,对于抑制电磁耦合噪声至关重要。

225kV镀膜电源纹波抑制的研究与实践,是一个涉及电力电子、电磁兼容、材料学和真空等离子体工艺的交叉课题。通过综合运用上述技术,可以将输出电压纹波系数(峰峰值/直流值)从百分之几降低至千分之一甚至更低的水平,为制备高品质、高性能的功能薄膜提供近乎纯净的直流高压环境,是高端镀膜装备核心技术竞争力的重要体现。