静电卡盘高压电源稳定性对半导体制造良率的影响分析

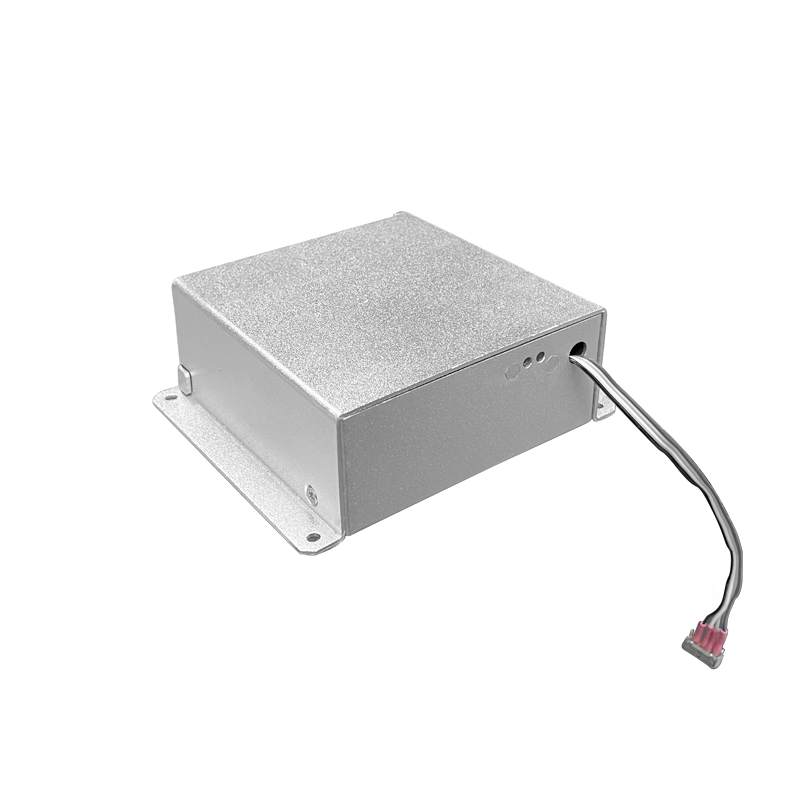

在当代半导体制造的核心工艺设备中,如等离子体刻蚀机与化学气相沉积设备,静电卡盘已成为固定与控温晶圆的关键部件。其工作原理是通过向内部电极施加数百至数千伏的直流高压,在卡盘表面与晶圆背面之间产生强大的静电力,从而实现对晶圆的非机械式夹持。这一夹持过程的有效性、稳定性与均匀性,直接决定了晶圆在工艺腔室内所经历的热传导条件、等离子体鞘层电位分布以及物理应力状态,进而对刻蚀或沉积的均匀性、特征尺寸控制以及缺陷产生概率产生深远影响。而静电卡盘性能的基石,正是为其提供吸附电压的高压直流电源的稳定性。这种稳定性并非简单的电压不漂移,而是包含了多重维度的精密要求,任何维度的偏离都可能成为良率损失的隐形杀手。

首先,高压电源输出电压的绝对精度与长期漂移,直接影响吸附力的设定值与保持力。在先进制程中,晶圆厚度不断减小,翘曲度可能增加,同时工艺温度可能高达数百摄氏度。为了在各种工况下都能可靠吸附并避免滑片,所需的最佳吸附电压是一个需要精细优化的参数。若电源的输出电压存在系统性偏差或随时间缓慢漂移,实际施加的电压将偏离工艺工程师设定的最优值。电压过低可能导致吸附力不足,在工艺过程中(尤其是存在射频偏压或机械振动时)发生晶圆微动甚至滑移,这直接导致图形错位或整个晶圆的报废。电压过高则可能使吸附力过大,增加晶圆背面的机械应力,在高温下可能诱发晶格缺陷或滑移线,对于超薄晶圆尤为危险;同时,过高的电场也可能增加卡盘介电层击穿的风险,引发微放电,在晶圆背面产生缺陷。

其次,输出电压的纹波与噪声是另一个关键但常被忽视的因素。理想的吸附电压应为纯净的直流。然而,任何实际电源都存在一定程度的交流纹波和随机噪声。这些交流分量叠加在直流高压上,会产生周期性的静电力脉动。这种脉动虽然平均力可能不变,但其动态效应可能带来多重危害。其一,它可能激发晶圆或卡盘结构的微小谐振,导致晶圆与卡盘表面之间产生微米甚至纳米级的周期性间隙波动。在等离子体工艺中,这个微小间隙的变化会显著改变该区域的热传导(氦气冷却)效率和局部等离子体鞘层特性,导致该区域的刻蚀速率或沉积速率出现周期性异常,在晶圆上形成难以诊断的、具有空间周期性的缺陷图案。其二,高频噪声可能通过容性耦合干扰晶圆背面的测温传感器(如热敏电阻)信号,导致温控系统误判,引起实际工艺温度失控。

再者,高压电源的动态响应特性与负载调整率,决定了其在工艺瞬态过程中的表现。半导体工艺并非全程稳态,例如在射频功率开启/关闭、工艺步骤切换、腔室抽充气等瞬间,等离子体阻抗和晶圆背面的电气接触条件可能发生快速变化。这相当于静电卡盘的等效负载在动态变化。一个动态响应不佳的电源,其输出电压会随着负载变化而波动。如果电压在瞬态过程中跌落,吸附力瞬时减弱,可能引发晶圆位置微扰;如果出现电压过冲,则可能带来瞬间过应力。此外,在双极型静电卡盘中,需要定期进行电压极性反转以释放残留电荷,这个切换过程的快慢、平滑度以及切换后的稳定性,都对避免晶圆扰动和电荷积累损伤至关重要。

从良率损失的路径来看,由高压电源稳定性问题引发的缺陷往往具有隐蔽性和系统性。它们可能表现为:片内均匀性变差(如刻蚀速率或薄膜厚度的径向分布异常);随机出现的单点缺陷(由微放电或瞬时滑移引起);整批性的参数漂移(由电源的长期慢漂移导致);以及难以复现的间歇性工艺失败。由于这些缺陷根植于电源这一底层子系统,其排查和诊断往往需要深入到设备厂商的维护层面,耗费大量机时与工程资源。

因此,在半导体设备选型与日常监控中,对静电卡盘高压电源的稳定性评估必须建立一套严格的量化指标体系。这应包括:电压设定精度(如±0.1%)、长期漂移(如24小时内<0.05%)、峰峰值纹波电压(如<0.1% of Vout)、负载调整率(从空载到满载输出电压变化<0.1%)、电压建立时间及过冲、极性切换时间与稳定性等。定期的预防性维护与校准,必须将高压电源的关键参数作为必检项。更先进的做法是在设备运行过程中,通过数据采集系统持续监测电源的输出电压与电流波形,利用大数据分析手段建立其健康基线,实现对性能劣化的早期预警。

综上所述,静电卡盘高压电源的稳定性,是半导体制造工艺中一个深藏不露却又举足轻重的环节。它如同建筑物的地基,其微小的不均匀沉降足以导致上部精密结构的整体失效。在追求单个原子层级别工艺控制的先进制程中,对静电力这一基础作用力的精准、稳定控制,已容不得丝毫妥协。确保高压电源在全生命周期内保持卓越的稳定性,是保障芯片制造高良率、高可靠性的底层硬件基石之一。