电子束直写系统多通道高压电源的串扰与同步误差校正

电子束直写技术是纳米光刻工艺中的关键环节,它通过聚焦的电子束在涂有抗蚀剂的晶圆上直接描画电路图形,具有极高的分辨率和灵活性,广泛应用于掩模版制造、先进工艺研发及特殊器件加工。现代多电子束直写系统为实现高通量,采用成千上万个独立可控的微小电子束并行工作,每个电子束都需要一套独立的高压电源来精确控制其加速、聚焦和偏转。在这些电源密集排布、协同工作的环境下,通道间的串扰和同步误差成为影响最终光刻套刻精度和分辨率的两大核心电气挑战。

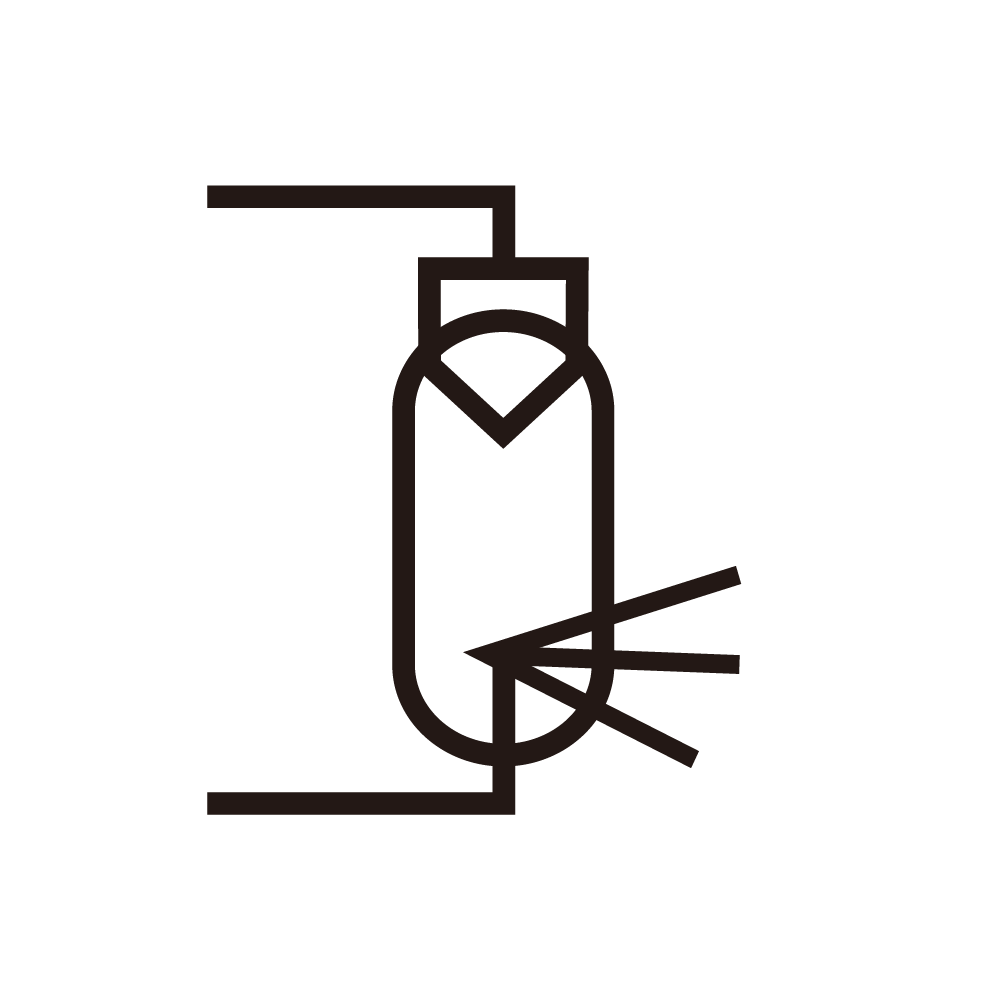

通道间串扰,是指一个高压电源通道的输出波动,通过电磁耦合的方式,影响到相邻或其他通道的输出稳定性。在电子束直写系统中,加速电压的任何微小扰动都会直接导致束斑能量变化,影响曝光剂量;而聚焦透镜或偏转器电压的扰动,则会直接导致束斑位置偏移,造成图形畸变。串扰的路径主要包括:公共阻抗耦合(如共用的地线或电源线)、电场耦合(分布电容)和磁场耦合(互感)。在多通道、高密度布线的系统中,这些寄生效应被急剧放大。例如,当一个束流的偏转器电压快速变化时,其电压变化率dV/dt通过寄生电容,会在相邻束流的偏转器线上感应出干扰电流,导致后者电压波动。

为了抑制串扰,设计需从源头、路径和接收端多管齐下。源头措施是降低每个通道自身的输出噪声和开关边沿速率。采用软开关技术和多级滤波,使电源输出本身就是一个“洁净”的源。路径隔离是核心。首先,必须实现极低阻抗的接地系统,采用多点接地或混合接地策略,并利用大面积接地平面来最小化公共阻抗。其次,所有高压输出线必须使用具有良好屏蔽的同轴电缆,且屏蔽层必须在电源端和负载端(电子枪端)都实现360°的可靠接地。在多层PCB设计中,高压信号线应与低压控制线严格分区,并用地线或接地层进行隔离。对于敏感的模拟反馈电路,应采用独立的屏蔽盒进行局部封装。在空间布局允许的情况下,应增加通道间的物理距离。

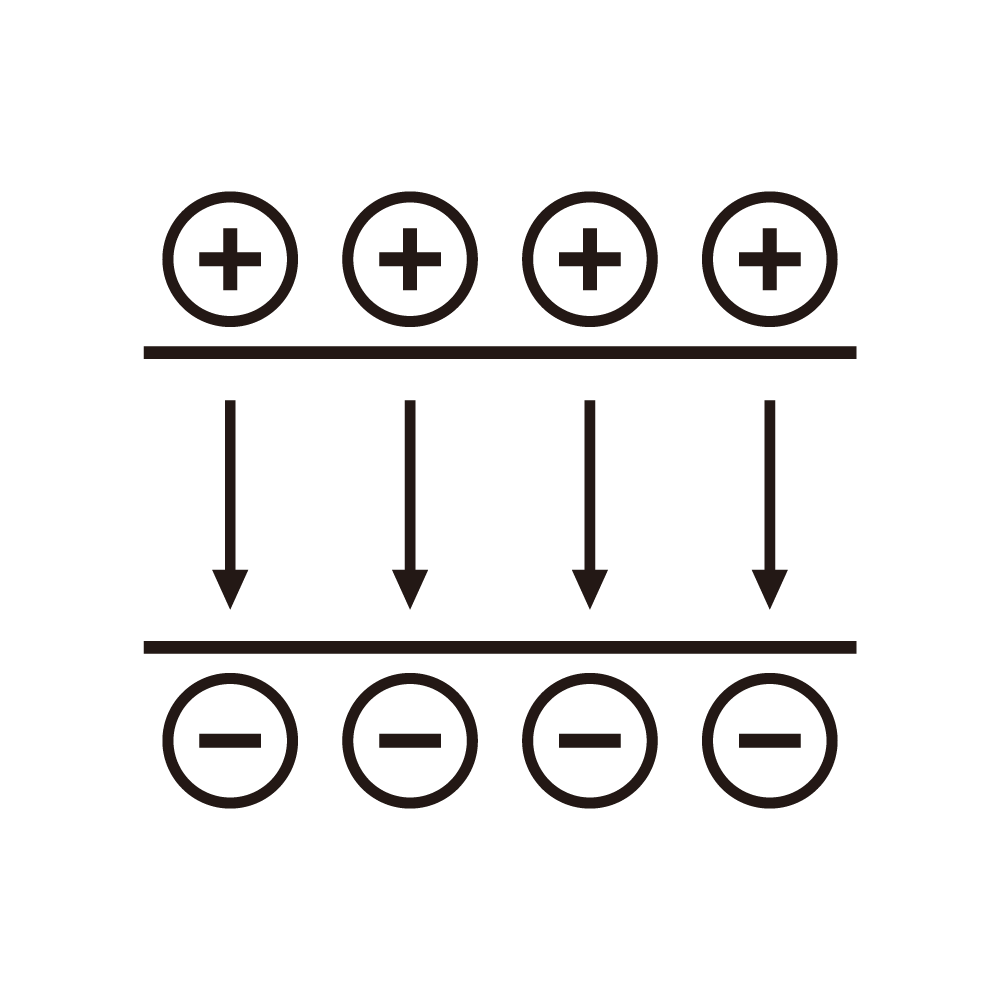

同步误差校正,则主要针对需要时序协调的偏转和扫描操作。在多电子束系统中,不同束流可能被要求同时或按一定相位差进行扫描,以拼接出一幅完整的图形。如果驱动各束流偏转器的高压电源的时基不同步,或者其输出在响应同一触发信号时存在不同的延迟,就会导致各个束斑的实际扫描轨迹在时间和空间上错位,在图形拼接处产生重叠或间隙,破坏图形完整性。

实现精确同步,首先需要一个高精度、低抖动的全局时钟源,通过分布式的时钟树将时钟信号同时分发到每一个通道的控制器。每个通道的电源控制器内部的数模转换器、PWM发生器等关键时序单元,都必须与这个全局时钟同步。其次,需要对通道间的输出延迟进行精确测量和补偿。即使电路设计再理想,不同通道因元器件参数的微小差异,其信号路径延迟仍会有细微差别。因此,系统需要具备自校准能力:在系统启动或定期维护时,可以向所有通道同时施加一个标准的阶跃或脉冲指令,并通过一个高速多路复用器和高精度采样电路,测量每个通道实际输出电压相对于参考通道的延迟时间。测得的延迟误差表被存入存储器,在实际工作中,控制系统根据这张表,为每个通道的指令添加一个负延迟或调整其触发相位,以补偿这些固有误差,实现真正的同步输出。

更高阶的校正涉及动态跟踪。随着工作温度和电源老化,通道的延迟特性会发生缓慢漂移。因此,一些高端的系统会在工作间隙,插入短暂的校准脉冲序列,进行在线的、非侵入式的延迟重测和修正。

此外,数字控制与信号处理技术的进步也为串扰抑制和同步校正提供了新手段。例如,通过在FPGA内实现数字预失真或前馈补偿算法,可以根据预设的干扰模型,主动在指令信号上叠加一个微小的反向补偿量,以抵消预期的串扰影响。同样,也可以通过数字延迟线实现极高分辨率的触发相位微调。

总之,在电子束直写系统这一精密电子光学平台中,多通道高压电源的设计已超越传统的功率变换范畴,演变为一个涉及精密模拟电路、高速数字逻辑、电磁场分析和先进控制理论的系统工程。对串扰和同步误差的极致抑制与校正,是确保成千上万束流能够步调一致、精确无误地共同绘制纳米电路蓝图的电气基础,其技术水平直接定义了光刻系统的产能与精度边界。