单光子雪崩二极管阵列偏置高压电源的通道间串扰抑制

单光子雪崩二极管阵列是激光雷达、量子通信及荧光寿命成像的核心探测器,其工作在盖革模式——偏置电压高于击穿电压,单个光子即可触发雪崩,产生可探测电流脉冲。为满足高像素需求,阵列规模已达数百至数千单元,每个单元需独立偏置或分组偏置。高压电源为阵列提供击穿电压以上的偏压,其稳定性与噪声直接影响探测效率与暗计数。更为棘手的是,通道间串扰——一个像素雪崩时,其电流脉冲通过公共偏置线耦合至相邻像素,引起误触发。通道间串扰抑制是单光子雪崩二极管阵列高压电源设计的核心挑战。

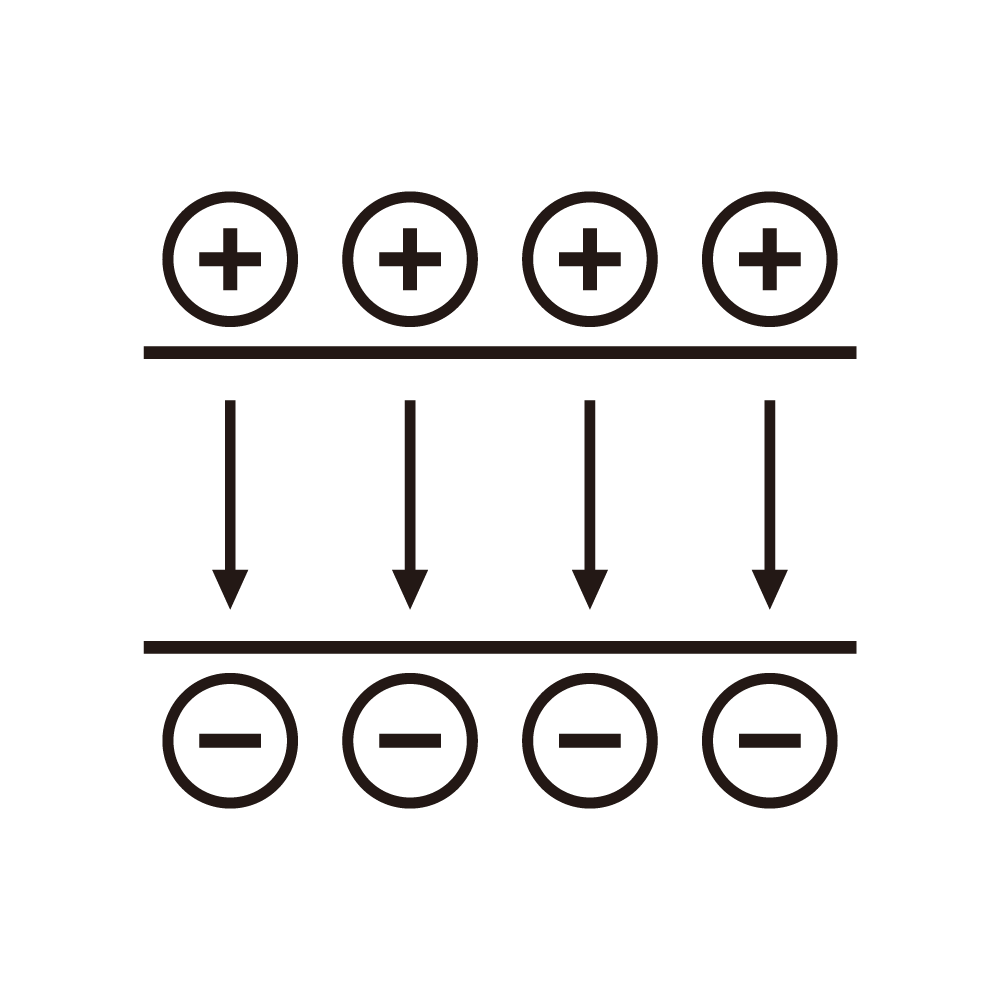

串扰的物理机制包括电阻耦合与电容耦合。公共偏置线存在寄生电阻,当某一像素雪崩时,大电流(毫安级)在电阻上产生压降,使公共偏置点电位瞬间下降,相邻像素偏压随之下降,若低于击穿电压,则无法探测光子;若下降后又恢复,可能引起振铃,误触发相邻像素。电容耦合源于像素间寄生电容,雪崩脉冲的快速前沿通过电容微分耦合至相邻像素,产生尖峰干扰。

抑制串扰的首要策略是降低公共偏置线阻抗。采用厚金属布线,增大导线截面积,减小电阻。对于大型阵列,可采用多层供电网络——主偏置线分布于芯片外围,通过多个分支点接入各像素,使每个像素的供电路径电阻一致且最小。电源输出端需配置大容量储能电容,就近布置于芯片附近,为雪崩瞬间提供瞬态电流,减小偏置线压降。储能电容需低等效串联电阻,通常采用多层陶瓷电容并联。

有源钳位是抑制电容耦合的有效手段。在每个像素的偏置输入端设置钳位二极管,当雪崩引起电位下降时,钳位二极管导通,将下降幅度限制在0.7伏以内,防止过深下降。钳位二极管的恢复速度需快于雪崩脉冲,通常采用肖特基二极管,其反向恢复时间可忽略。对于更高要求,可采用有源钳位电路——运算放大器检测偏置点下降,驱动晶体管快速补充电荷,使偏置点几乎不变。

像素间隔离设计需从版图层面优化。增大像素间距,减小寄生电容,但会降低填充因子。采用深沟槽隔离,在像素间刻蚀深槽填充绝缘材料,切断电容耦合路径。对于背照式阵列,可将偏置线布置于芯片背面,与正面像素通过硅通孔连接,进一步减小正面耦合。

高压电源的纹波与噪声也是串扰的来源。电源输出纹波通过公共偏置线耦合至所有像素,使各像素偏压同步波动,但不会引起像素间差异。然而,若电源输出阻抗过高,纹波在偏置线上产生空间分布,引起像素间偏压差异。因此,电源需具备低输出阻抗,通常采用线性稳压后级,使输出阻抗小于0.1欧姆。

在阵列测试中,通道间串扰抑制的效果通过串扰概率评估——向单一像素照射光子,测量相邻像素的响应计数。理想情况下串扰概率应小于0.1%。某256×256单光子雪崩二极管阵列,采用上述抑制措施后,串扰概率从5%降至0.3%,满足量子成像应用需求。阵列探测效率25%,暗计数率100赫兹,性能达到国际先进水平。

展望未来,随着阵列规模向百万像素发展,串扰抑制需更精细化。基于数字辅助的串扰抵消技术——在读出电路中记录雪崩发生时间与位置,通过算法识别并剔除串扰事件,可与硬件抑制互补。高压电源将向片上集成方向发展,将偏置稳压器与钳位电路直接集成于像素阵列边缘,使供电路径缩短至毫米级,从根本上消除串扰。